# PI409MC-A4 400DPI CIS Module Engineering Data Sheet

#### **Key Features**

- Light source, lens, and sensor are integrated into a single module

- Ultra-High-Speed

- Four parallel analog video outputs clocked at 5.0MHz.

- 180 µsec/line scanning speed @ 5.0 MHz clock speed

- 15.8 dpm resolution, 216 mm scanning length

- Wide dynamic range

- Red light source 660nm

- Low power

- Light weight

## **General Description**

The PI409MC-A4 is a CIS module. It is a long contact image sensor modules, using MOS image sensor technology for high-speed performance and high sensitivity. Its four parallel video outputs gives the PI409MC-A6 its high speed performance. The PI409MC-A4 is suitable for scanning A4 size (216 mm) documents with 15.8 dots per millimeter resolution. Applications include document scanning, mark readers, gaming and office automation equipment.

## **Functional Description**

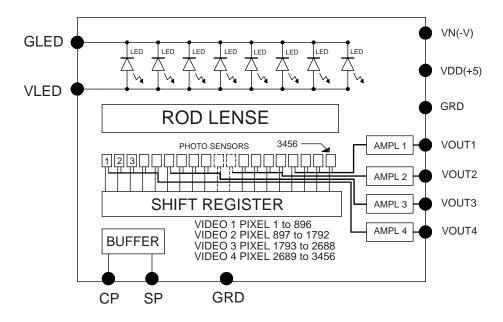

The PI409MC-A4 imaging module consists 27 imaging chips, PI3022, produced by Peripheral Imaging Corporation. The sensor chips are monolithic devices with 128 photo

sensing elements. Twenty seven of these imaging chips are cascaded to provide 3456 photo-elements module. The PI3022 chips are integrated with the photo sensors' associated multiplex switches, a digital shift register and chip selection switch. The shift register sequentially clocks out the integrated image charges from each sensing elements and passes them through the chip-select switch and out onto the video line. The chip-select switch are sequentially switched as each of the predecessor chip completes its scan. These 27 sensors bonded on a PCB are grouped into 4 sub-cascaded sections. Each contiguously cascaded chips section are connected on separate video lines, accordingly providing four video outputs VOUT1, VOUT2, VOUT3 and VOUT4. Before the signal charges from the four video lines appear at their respective outputs they are converted to signal voltages by four on-board buffer amplifiers, one for each of its corresponding video section. The first three sections VOUT1, VOUT2, and VOUT3 have 7 sensor chips, while the VOUT4 has 6 sensor chips. Since each sensor chip have 128 pixels, there are total of 3456 pixels. See Figure 1. PI409MC-A4 Module Block Diagram.

Figure 1. PI409MC-A4 Module Block Diagram (See Table 1 for pin-out designation)

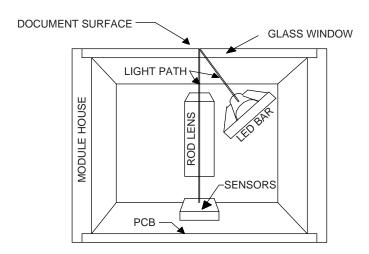

Mounted in the module housing, along with the PCB, is a one-to-one graded indexed micro lens array that focuses the scanned documents' image onto the sensing line of the sensor chips. The third major component mounted in the module is the LED light source. See Figure 2. PI409MC-A4 Cross Sectional View. The pictorial cross section shows the LED Bar light source and its Illumination path as it reflects the image from the document and focuses through the ROD lens on to its image sensing line of the sensing chips. All components are housed in a small plastic housing that has a cover glass. This cover glass is, also, the window. It serves as the focal point for the object being scanned, as well as to protect all of the critical components with the housing from dust. I/O to the module is

a 12-pin connector located on one end of the module. See Figure 5. Module's Mechanical Overview.

INSIDE PICTORIAL OF MODULE

Figure 2. PI409MC-A4 Cross Section

# I/O Designation

Table 1 lists the pin numbers and their designations for the I/O connector. It is JAE IL-Z-12P-S125L3-E connector.

| Pin Number | Symbol    | Names and Functions             |

|------------|-----------|---------------------------------|

| 1          | VOUT1     | Analog Video Output 1           |

| 2          | VOUT2     | Analog Video Output 2           |

| 3          | GND       | Ground; 0V                      |

| 4          | VOUT3     | Analog Video Output 3           |

| 5          | VOUT4     | Analog Video Output 4           |

| 6          | Vdd       | Positive power supply           |

| 7          | SP(START) | Shift register start pulse      |

| 8          | GND       | Ground; 0V                      |

| 9          | CP(CLOCK) | Sampling clock pulse            |

| 10         | Vn        | Negative power supply           |

| 11         | GLED      | Ground for the light source; 0V |

| 12         | VLED      | Supply for the light source     |

Table 1. Pin configuration

# **Absolute Maximum Rating:**

| Parameter         | Symbols | Maximum Rating | Units |

|-------------------|---------|----------------|-------|

| Power supply      | Vdd     | 7              | V     |

| voltage           | ldd     | 100            | ma    |

|                   | Vn      | -15            | V     |

|                   | In      | 35             | ma    |

|                   | VLED    | 6              | V     |

|                   | ILED    | 600            | ma    |

| Input clock pulse | Vih     | Vdd - 0.5V     | V     |

| (high level)      |         |                |       |

| Input clock pulse | Vil     | -0.5           | V     |

| (low level)       |         |                |       |

Note: These parameters are absolute maximums do not operate under these conditions.

Table 2. Absolute Maximum Rating

## **Environmental Specifications**

| Operating                       | Тор  | 0 to 50   | °C |

|---------------------------------|------|-----------|----|

| temperature(1)                  |      |           |    |

| Operating                       | Нор  | 10 to 90  | %  |

| humidity <sup>(1)</sup>         |      |           |    |

| Storage                         | Tstg | -20 to+75 | 0C |

| temperature(1)                  |      |           |    |

| Storage humidity <sup>(1)</sup> | Hstg | 10 to 90  | %  |

Table 3. Operating and Storage Environment Note (1) These are standard specifications for the CIS modules.

## Electro-Optical Characteristics (25°C)

| Parameter                      | Symbol              | Parameter | Units    | Note      |

|--------------------------------|---------------------|-----------|----------|-----------|

| Total number of photo          |                     | 3456      | Elements |           |

| detectors                      |                     |           |          |           |

| Section 1, 2, & 3 number       |                     | 896       | Elements |           |

| of photo detectors             |                     |           |          |           |

| Section 4 number of            |                     | 768       | Elements |           |

| detectors                      |                     |           |          |           |

| Pixel-to-pixel spacing         |                     | 63.5      | μm       |           |

| Line scanning rate             | Tint <sup>(1)</sup> | 180       | μsec     | @ 5.0MHz  |

| _                              |                     |           |          | clock     |

|                                |                     |           |          | frequency |

| Clock frequency <sup>(2)</sup> | f                   | 5.0       | MHz      |           |

| Bright output voltage(3)       | Video Output        | 500       | mVolt    |           |

| Bright output                      | Up              | +/-30 | %  |

|------------------------------------|-----------------|-------|----|

| nonuniformity <sup>(4)</sup>       |                 |       |    |

| Dark nonuniformity <sup>(5)</sup>  | Ud              | <140  | mV |

| Dark output voltage <sup>(6)</sup> | Dark Level (DL) | <600  | mV |

| Modulation transfer                | MTF             | >50   | %  |

| function <sup>(7)</sup>            |                 |       |    |

Table 4. Electro-optical characteristics at 25° C.

#### Definition:

- (1) Tint: line scanning rate or integration time. Tint is determined by the interval between two start pulses (SP).

- (2) f: main clock frequency also equals the video sampling frequency.

- (3) Video output level is controlled with an adjustment as well as Integration time

- (4) Up = {[Vp(max) -Vp(min)]/Vp(max)}x100%

- Where Vp(max) = maximum peak pixel and <math>Vp(min) = minimum pixel.

- (5) Ud = Vdmax Vdmin

Vdmin is the minimum output voltage with LED off.

Vdmax is maximum output voltage with LED on.

- (6) This level is measured from the reset level that is located between the pixels, during the pixel reset duration. The reset level is at or near ground, 0V. Note the gain is adjustable on each output. However, it is recommended that the gain should not be increased above the level where the reset ground level starts to increase above zero.

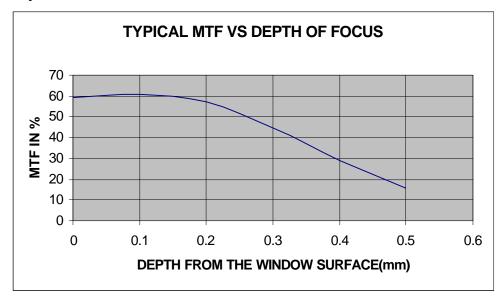

- (7) A graph of the typical is shown under discussion of MTF in Figure 3.

### **MTF Graph and Its Discussion**

Figure 3. MTF versus Distance

See Figure 3 MTF versus Distance. This graph essentially shows the working depth of focus. Since this module is a 400DPI module, a pixel density of 400 pixel per inch, the

MTF was measured with a 200 DPI or a 100 line-pair per inch optical bar pattern. The test was conducted with pixel rate set to 2.5MHz.

The effective algorithm used in the measurements is as described by the following equation:

MTF={[Vp(n)+Vp(n+1)]/2-[Vp(n+2)+Vp(n+3)]/2}/{[Vp(n)+Vp(n+1)]/2+[Vp(n+2)+Vp(n+3)]/2} Where n is 1, 2, .....3456<sup>th</sup>, Vp(n) is the signal amplitude of the n<sup>th</sup> pixel.

## Recommended Operating Conditions (25°C)

| Item                                 | Symbol | Min     | Typical | Max  | Units |

|--------------------------------------|--------|---------|---------|------|-------|

| Power Supply                         | Vdd    | 4.5     | 5.0     | 5.5  | V     |

|                                      | Vn.    | -13     | -5      | -4.0 | V     |

|                                      | ldd    |         | 87      | 95   | ma    |

|                                      | In     |         | 25      | 30   | ma    |

|                                      | ILED   |         | 450     | 550  | ma    |

|                                      | VLED   |         | 5       | 5.5  | V     |

| Input voltage at digital high        | Vih    | Vdd-1.0 | Vdd5    | Vdd  | V     |

| Input voltage at digital low         | Vil    | 0       |         | 0.6  | V     |

| Clock frequency                      | f      | 0.      | 5.0     | 6.0  | MHz   |

| Clock pulse high duty cycle          |        |         | 25      |      | %     |

| Clock pulse high duration            |        |         | 50      |      | ns    |

| Integration time                     | Tint   |         | 180     |      | μs    |

| Operating temperature <sup>(1)</sup> | Тор    |         | 25      | 50   | °C    |

Table 5. Recommended Operating Condition (25 °C) Note (1) see the note under the Table for Operating and Storage Environment.

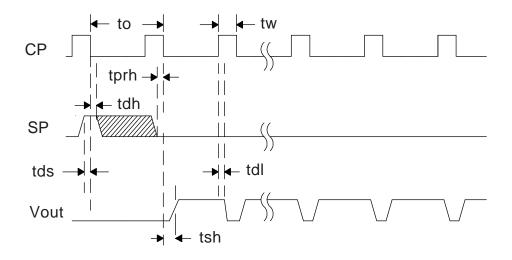

## Switching Characteristics (25°C)

The Switching Characteristics (25°C) for the I/O clocks are shown in the diagram Figure 4, on the following page. For the timing symbol definitions see Table 6 below the timing diagram. Note: Only one video output is shown because all four videos have identical electrical characteristic. The only physical difference is in section 4 output,VOUT4. Section 4 has only 6 sensor chips, hence, its active scan is shorter by 128 pixels.

# MODULE TIMING DIAGRAM FIGURE 4

| Item                                                 | Symbol | Min. | Typical | Max. | Units |

|------------------------------------------------------|--------|------|---------|------|-------|

| Clock cycle time                                     | to     | 0.20 |         | 4.0  | μs    |

| Clock pulse width                                    | tw     | 50   |         |      | ns    |

| Clock duty cycle                                     |        | 25   |         | 75   | %     |

| Prohibit crossing time of Start Pulse <sup>(1)</sup> | tprh   | 0    |         |      | ns    |

| Data setup time                                      | tds    | 20   |         |      | ns    |

| Data hold time                                       | tdh    | 0    |         |      | ns    |

| Signal delay time                                    | tdl    | 20   |         |      | ns    |

| Signal settling time                                 | tsh    | 100  | _       |      | ns    |

Table 6. Timing Symbol's Definition and Timing Values.

#### Note1:

"Prohibit crossing of start pulse" is to indicate that the start pulse should not be active high between any two consecutive high going clock pulse or two consecutive low going clock pulses. See the timing diagram. Only one high going clock under the active high start pulse initiates the internal shift register, and it must not be active over two high going clocks. All low going clock pulses will not initiate the shift register. To ensure that the start pulse will not be actively high during two consecutive high going clocks, the circuit should be design to keep the start pulse active only for one high going clock cycle.

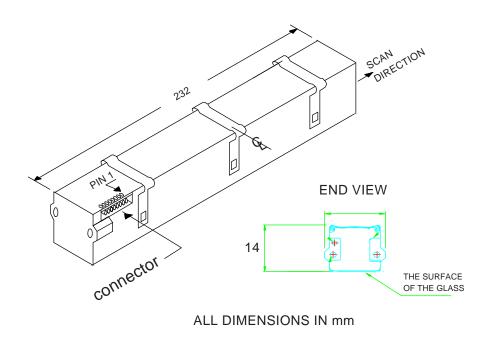

#### Mechanical Structure of the Module

The isometric sketch, Figure 5, of the housing is shown to demonstrate the connector location, the approximate overall dimensions and its general geometric layout of the module. It is not intended for use as a design reference. The detailed drawing for the PI409MC-A4 Module Housing is available upon request.

Figure 5. PI409MC-A4 Module Housing Sketch

©2000 Peripheral Imaging Corporation. Printed in USA. All rights reserved. Specifications are subject to change without notice. Contents may not be reproduced in whole or in part without the express prior written permission of Peripheral Imaging Corporation. Information furnished herein is believed to be accurate and reliable. However, no responsibility is assumed by Peripheral Imaging Corporation for its use nor for any infringement of patents or other rights granted by implication or otherwise under any patent or patent rights of Peripheral Imaging Corporation.